# Vivado Design Suite Tutorial

Partial Reconfiguration on

Zed Board

\*This document is based on the Xilinx document UG947: Vivado Design Suite Tutorial on Partial Reconfiguration

# Table of Contents

| 1 | Objective | es                                     | . 2 |

|---|-----------|----------------------------------------|-----|

| 2 | Vivado P  | artial Reconfiguration - Documentation | , 2 |

| 3 | Tutorial  |                                        | . 2 |

|   | 3.1 Led   | Shift Count                            | . 2 |

|   | 3.1.1     | Extract the Tutorial Design files      | . 2 |

|   | 3.1.2     | Synthesize the Design                  | . 2 |

|   | 3.1.3     | Assemble the Design                    | .3  |

|   | 3.1.4     | Build the Design Floorplan             | .6  |

|   | 3.1.5     | Implement the First Configuration      | .8  |

|   | 3.1.6     | Implement the Second Configuration     | 10  |

|   | 3.1.7     | Generate Bitstreams                    | 10  |

|   | 3.1.8     | Partial Reconfiguration of the FPGA    | 11  |

### 1 Objectives

- Implement a project that can be dynamically reconfigured using the Zed Board.

- Learn the Partial Reconfiguration (PR) flow with the Vivado TCL console.

# 2 Vivado Partial Reconfiguration - Documentation

- UG909: Vivado Design Suite User Guide Partial Reconfiguration.

- UG947: Vivado Design Suite Tutorial Partial Reconfiguration. You can follow this for the Xilinx-provided ug947-vivado-partial-reconfiguration-tutorial.zip file (this is a Verilog design for the KC705 demonstration board)

# 3 Tutorial

### 3.1 Led Shift Count

### 3.1.1 Extract the Tutorial Design files

• Extract the zip file contents from Dynamic\_PR\_Tutorial to any write-accessible location.

### 3.1.2 Synthesize the Design

- Open the Vivado TCL Shell. Navigate to the /led\_shift\_count\_directory.

- Run the design.tcl script by entering: **source design.tcl –notrace.** This will Synthesize the design and create output files in the /Synthesis folder. The 'top' design will be created with a blank circuit for the Reconfigurable Partition.

\*\*\*\*\* Vivado v2015.2 (64-bit) \*\*\*\* SW Build 1266856 on Fri Jun 26 16:35:25 MDT 2015 \*\*\*\* IP Build 1264090 on Wed Jun 24 14:22:01 MDT 2015 \*\* Copyright 1986-2015 Xilinx, Inc. All Rights Reserved.

Vivado% cd E:/Grad\_Project/led\_shift\_count Vivado% source design.tcl -notrace

Fig 1. Vivado TCL Shell

#### 3.1.3 Assemble the Design

• Open the Vivado IDE by entering **start\_gui** in Vivado TCL Shell.

```

Vivado 2015.2 Tcl Shell - E:\Xilinx\Vivado\2015.2\bin\vivado.bat -mode tcl

on Sat Feb 06 14:03:45 2016. For additional details about this file, please ref

er to the WebTalk help file at E:/Xilinx/Vivado/2015.2/doc/webtalk_introduction.

html.

INFO: [Common 17-206] Exiting Webtalk at Sat Feb 06 14:03:45 2016...

close_project: Time (s): cpu = 00:00:00 ; elapsed = 00:00:46 . Memory (MB): peak

= 529.230 ; gain = 0.000

#HD: Synthesis of module Static complete

#HD: Running synthesis for block shift_right

Writing results to: ./Synth/shift_right

#HD: Setting Tcl Params:

hd.visual == 1

Ε

Info: No XDC file specified for shift_right

Running synth_design

#HD: Synthesis of module shift_right complete

#HD: Running synthesis for block shift_left

Writing results to: ./Synth/shift_left

#HD: Setting Icl Params:

hd.visual == 1

Info: No XDC file specified for shift_left

Running synth_design

#HD: Synthesis of module shift_left complete

#HD: Running synthesis for block count_up

Writing results to: ./Synth/count_up

#HD: Setting Icl Params:

hd.visual == 1

Info: No XDC file specified for count_up

Running synth_design

#HD: Synthesis of module count_up complete

Info: No XDC file specified for count_down

Running synth_design

#HD: Synthesis of module count_down complete

#HD: Sorted list of configurations:

Config_shift_right_count_up

(Static: implement

Implement: 0

Verify: Ø

Bitstrea

m: 0)

Config_shift_left_count_down

(Static: import

Implement: 0

Verify: Ø

Bitstrea

m: 0)

Skipping pr_verify for Configuration Config_shift_left_count_down with a

ttribute "verify" set to '0'

Skipping write_bitstream for Configuration Config_shift_right_count_up w

ith attribute "bitstream" set to '0'

Skipping write_bitstream for Configuration Config_shift_left_count_down

with attribute "bitstream" set to '0'

Vivado% start_gui

```

Fig 2. Vivado TCL Shell after sourcing the design.tcl file

• Load the static design by issuing the following command in the Tcl Console:

| Manag       | ge IP Open                                                                               | n Hardware Manager                                                                                 |                                      | inx Tcl Sta                  | )<br>ж            | top_route_desig<br>Implement/Conf<br>top_route_desig | fig_shift_left_cou                       | in             |

|-------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------|-------------------|------------------------------------------------------|------------------------------------------|----------------|

| Tcl Console |                                                                                          |                                                                                                    |                                      |                              |                   |                                                      | _ C                                      | ле×            |

| Con         | nfig_shift_left_<br>(Static: import<br>ipping pr_verify<br>ipping write_bit<br>start_gui | for Configurations<br>for Configurations<br>stream for Configurations<br>stream for Configurations | 0 V<br>on Conf<br>guratic<br>guratic | Verify:<br>Sig_shitten Conf: | 0<br>ft_l<br>ig_s | hift_right_                                          | 0)<br>0)<br>Dwn with att<br>count_up wit | ribut<br>h att |

| open_chec   | kpoint Synth/St                                                                          | atic/top_synth.dc                                                                                  | þ                                    |                              |                   |                                                      |                                          |                |

#### open\_checkpoint Synth/Static/top\_synth.dcp

| File Edit Flow Tools Window Layout Yew Help                                                                                                                                                  |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 🟄 🔂 🖩 🕼 🖉 🤚 🦍 X 🛷 🕅 🧐 🥝 😵 🚱 🔛 Default Layout 💿 👻 🛞                                                                                                                                           |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Checkpoint Design - xc7z020dg484-1                                                                                                                                                           |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Netist _ 🗆 🕑 ×                                                                                                                                                                               | Sevice X C                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| № top<br>⊕ - Control (162)                                                                                                                                                                   |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| 🕀 🔚 Leaf Cells (92)                                                                                                                                                                          | ←                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              | <u>₩112</u>                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Properties _ 🗆 ど ×                                                                                                                                                                           | ∑<br>X0Y1 X1Y1 ≤ ≤ ≤                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| ← → 100 k                                                                                                                                                                                    |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Select an object to see properties                                                                                                                                                           | ≥1,<br>X0Y0 X1Y0 <                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Td Console                                                                                                                                                                                   | <br>                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| INFO: [Project 1-570] Preparing netlist for logic of                                                                                                                                         |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| CRITICAL WARNING: [Project 1-486] Could not resolve                                                                                                                                          | non-primitive black box cell 'count' instantiated as 'inst_count' [E:/Grad_Project/led_shift_count/Sources/hdl/top/top.v:66]<br>non-primitive black box cell 'shift' instantiated as 'inst_shift' [E:/Grad_Project/led_shift_count/Sources/hdl/top/top.v:58] |  |  |  |  |  |  |  |

| INFO: [Project 1-111] Unisim Transformation Summary                                                                                                                                          |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| No Unisim elements were transformed.                                                                                                                                                         |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| INFO: [Project 1-484] Checkpoint was created with b                                                                                                                                          | nild 1266856                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| <pre>x into: project 1=451 (metapoint was cleared with bird redouse<br/>open_checkpoint: Time (s): cpu = 00:00:30 ; elapsed = 00:00:19 . Memory (MB): peak = 1253.305 ; gain = 120.289</pre> |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| checkpoint_top_synth                                                                                                                                                                         |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| ۲                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| E Td Console O Messages                                                                                                                                                                      |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                                                                                                              |                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

- You can see the design structure in the Netlist pane, but black boxes exist for the inst\_shift and inst\_count modules. Note that the Flow Navigator pane is not present. You are working in non-project mode.

- Two critical warnings are issued regarding unmatched instances. These instances are the Reconfigurable Modules that have yet to be loaded, and you can therefore ignore these warnings safely.

- Load the synthesized checkpoints for first Reconfigurable Module variants for each of reconfigurable partitions:

#### read\_checkpoint -cell inst\_shift Synth/shift\_right/shift\_synth.dcp

<u>Fi</u>le <u>E</u>dit Flow <u>T</u>ools <u>W</u>indow La<u>y</u>out <u>V</u>iew <u>H</u>elp Q- Search commands 孝 📄 📗 🕫 💷 🐘 🗙 🛷 🔄 🥝 🤡 🦉 😬 Default Layout 🔻 🗶 🔌 📜 🔍 Checkpoint Design - xc7z020dg484-1 Netlist \_ D & X ПĽХ Sevice X Z 🕅 🛃 ¥ top 🕅 🖲 🛅 Nets (162) Heaf Cells (92) inst\_count (co inst\_shift (shift) - D 🖻 🗡 Properties 🗲 🔶 🏷 ø Select an object to see properties Tcl Consol INFO: [DRC 23-27] Running DRC with 2 threads INFO: [Project 1-461] DRC finished with 0 Errors INFO: [Project 1-462] Please refer to the DRC report (report\_drc) for more information. INFO: [Opt 31-138] Pushed 0 inverter(s) to 0 load pin(s). 00 INFO: [DRC 23-27] Running DRC with 2 threads đ. INFO: [Project 1-461] DRC finished with 0 Errors INFO: [Project 1-462] Please refer to the DRC report (report\_drc) for more information. X INFO: [Opt 31-138] Fushed 0 inverter(s) to 0 load pin(s). checkpoint top synth Type a Tcl command here 📙 Tcl Console 🔘 Messages

#### read\_checkpoint -cell inst\_count Synth/count\_up/count\_synth.dcp

• Define each of these submodules as partially reconfigurable by setting the HD.RECONFIGURABLE property:

set\_property HD.RECONFIGURABLE 1 [get\_cells inst\_shift]

```

set_property HD.RECONFIGURABLE 1 [get_cells inst_count]

```

• Save the assembled design state for this initial configuration:

write\_checkpoint ./Checkpoint/top\_link\_right\_up.dcp

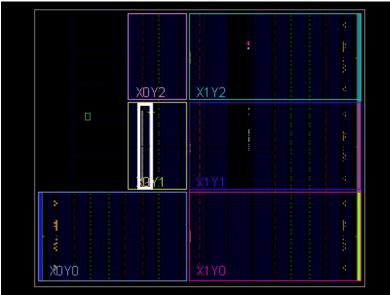

#### 3.1.4 Build the Design Floorplan

Here, you create a floorplan to define the regions that will be partially reconfigured.

• Select the inst\_count instance in the Netlist pane. Right click and select: **Floorplanning > Draw Pblock** and draw a tall narrow box. The exact size and shape do not matter at this point, but keep the box within the clock region.

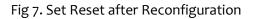

Fig 6. Draw Pblock for inst\_count

• In the Properties pane, select the checkbox for **RESET\_AFTER\_RECONFIG**. This will utilize the dedicated initialization of the logic in this module after reconfiguration has completed .

| Properties _ D Z X                                          |                                  |                                                                          |    |  |  |  |  |  |  |

|-------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------|----|--|--|--|--|--|--|

|                                                             |                                  |                                                                          |    |  |  |  |  |  |  |

| pblock_inst_count                                           |                                  |                                                                          |    |  |  |  |  |  |  |

| 0                                                           | CELL_COUNT                       | 1                                                                        | I] |  |  |  |  |  |  |

| $\mathbf{Z}$                                                | CLASS                            | pblock                                                                   |    |  |  |  |  |  |  |

|                                                             | CONTAIN_ROUTING                  |                                                                          |    |  |  |  |  |  |  |

|                                                             | DERIVED_RANGES                   | RAMB36_X2Y11:RAMB36_X2Y18, RAMB18_X2Y22:RAMB18_X2Y37, SLICE_X30Y52:SLICE |    |  |  |  |  |  |  |

| ∎ <sub>bbb</sub>                                            | EXCLUDE_PLACEMENT                |                                                                          |    |  |  |  |  |  |  |

| +                                                           | GRIDTYPES                        | SLICE RAMB18 RAMB36                                                      | 2  |  |  |  |  |  |  |

| $\times$                                                    | GRID_RANGES                      | RAMB36_X2Y11:RAMB36_X2Y18, RAMB18_X2Y22:RAMB18_X2Y37, SLICE_X30Y52:SLICE |    |  |  |  |  |  |  |

| ?                                                           | NAME                             | pblock_inst_count                                                        | 2  |  |  |  |  |  |  |

|                                                             | PARENT                           | ROOT                                                                     | 2  |  |  |  |  |  |  |

|                                                             | PARTPIN_SPREADING                | 5 🖉                                                                      | 2  |  |  |  |  |  |  |

|                                                             | PRIMITIVE_COUNT                  | 72                                                                       | 2  |  |  |  |  |  |  |

|                                                             | RECTANGLE_COUNT                  | 1                                                                        | L  |  |  |  |  |  |  |

|                                                             | RESET_AFTER_RECONFIG             |                                                                          |    |  |  |  |  |  |  |

|                                                             | SNAPPING_MODE                    |                                                                          |    |  |  |  |  |  |  |

|                                                             |                                  |                                                                          |    |  |  |  |  |  |  |

|                                                             |                                  |                                                                          |    |  |  |  |  |  |  |

| Gener                                                       | ral <b>Properties</b> Statistics | Cells Connectivity Rectangles                                            | -1 |  |  |  |  |  |  |

| General Properties Statistics Cells Connectivity Rectangles |                                  |                                                                          |    |  |  |  |  |  |  |

• Repeat the above to steps for inst\_shift instance.

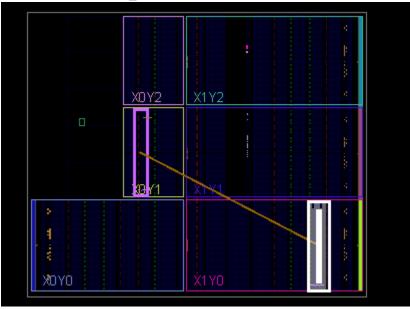

Fig 8. Draw Pblock for inst\_shift

• Run PR Design Rule Checks by selecting **Tools >Report >Report DRC**. You can uncheck **All Rules** and then check **Partial Reconfiguration** to focus this report strictly on PR DRCs.

| Check design against selected rule decks and/or individual design rules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Results name: drc_1 Output file: Rule Decks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| <ul> <li>Vivado Rule Decks (9)</li> <li>bitstream_checks</li> <li>default</li> <li>default</li> <li>eco_checks</li> <li>incr_eco_checks</li> <li>methodology_checks</li> <li>opt_checks</li> <li>placer_checks</li> <li>router_checks</li> <li>fining_checks</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Rules (59 of 4840)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Image: Psr (1)         Image: |    |

| ☑ Open in a new tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | el |

To avoid the DRC warning automatically by setting the SNAPPING\_MODE feature which automatically adjusts the size and shape of reconfigurable Pblocks to align with legal boundaries. It will make the Pblock taller, aligning with clock region boundaries, if the RESET\_AFTER\_RECONFIG feature is selected. It will make the Pblock narrower, adjusting left and/or right edges as needed. Note that the number and type of resources available will be altered if SNAPPING\_MODE makes changes to the Pblock.

| Pblock Properties _ D 🖓 ×                                   |                      |                                                                         |    |  |  |  |  |  |  |

|-------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|----|--|--|--|--|--|--|

|                                                             |                      |                                                                         |    |  |  |  |  |  |  |

| pblock_inst_shift                                           |                      |                                                                         |    |  |  |  |  |  |  |

| 0                                                           | CELL_COUNT           |                                                                         | 1  |  |  |  |  |  |  |

|                                                             | CLASS                | pblock                                                                  |    |  |  |  |  |  |  |

| <b>a</b>                                                    | CONTAIN_ROUTING      |                                                                         |    |  |  |  |  |  |  |

|                                                             | DERIVED_RANGES       | RAMB36_X5Y0:RAMB36_X5Y9, RAMB18_X5Y0:RAMB18_X5Y19, DSP48_X4Y0:DSP48_X4Y |    |  |  |  |  |  |  |

|                                                             | EXCLUDE_PLACEMENT    |                                                                         |    |  |  |  |  |  |  |

| <b>  +</b>                                                  | GRIDTYPES            | SLICE DSP48 RAMB18 RAMB36                                               | Ø  |  |  |  |  |  |  |

| ×                                                           | GRID_RANGES          | RAMB36_X5Y0:RAMB36_X5Y8, RAMB18_X5Y0:RAMB18_X5Y17, DSP48_X4Y0:DSP48_X4Y |    |  |  |  |  |  |  |

| ?                                                           | NAME                 | pblock_inst_shift                                                       | Ø  |  |  |  |  |  |  |

|                                                             | PARENT               | ROOT                                                                    | Ø  |  |  |  |  |  |  |

|                                                             | PARTPIN_SPREADING    | 5                                                                       | 50 |  |  |  |  |  |  |

|                                                             | PRIMITIVE_COUNT      |                                                                         | 5  |  |  |  |  |  |  |

|                                                             | RECTANGLE_COUNT      |                                                                         | 1  |  |  |  |  |  |  |

|                                                             | RESET_AFTER_RECONFIG |                                                                         |    |  |  |  |  |  |  |

|                                                             | SNAPPING_MODE        | DN                                                                      |    |  |  |  |  |  |  |

|                                                             |                      |                                                                         |    |  |  |  |  |  |  |

|                                                             |                      |                                                                         |    |  |  |  |  |  |  |

| General Properties Statistics Cells Connectivity Rectangles |                      |                                                                         |    |  |  |  |  |  |  |

#### Fig 10. Set Snapping mode

- Select the Pblock for inst\_count, and in the **Properties** tab of the Pblock Properties pane, change the value of SNAPPING\_MODE from OFF to ROUTING (or ON). Repeat same for inst\_shift instance. Then Run PR Design Check again.

- Save these Pblock definitions and its associated properties on a .xdc file:

#### write\_xdc ./Sources/xdc/fplan.xdc

#### 3.1.5 Implement the First Configuration

• Load the top-level constraint file by issuing the command:

#### read\_xdc Sources/xdc/top\_io.xdc

• Optimize, place, and route the design. Notice the Partition Pins (interface points between static and dynamic regions)

opt\_design

place\_design

route\_design

• Save the full design checkpoint and create report files:

write\_checkpoint -force Implement/Config\_shift\_right\_count\_up/top\_route\_design.dcp report\_utilization -file Implement/Config\_shift\_right\_count\_up/top\_utilization.rpt report\_timing\_summary –file Implement/Config\_shift\_right\_count\_up/top\_timing\_summary.rpt

At this point, you can use the static portion of this configuration for all subsequent configurations (variants of the circuit with different RMs for each RP). We need to isolate the static design by removing the Reconfigurable Modules:

Clear out Reconfigurable Module logic: update\_design -cell inst\_shift -black\_box update\_design -cell inst\_count -black\_box

Fig 11. Updated design

• Lock down all placement and routing. This is an important step to guarantee consistency for different RMs for each RP.

#### lock\_design -level routing

• Write out the remaining static-only checkpoint (this checkpoint will be used for any future configurations).

#### write\_checkpoint -force Checkpoint/static\_route\_design.dcp

#### 3.1.6 Implement the Second Configuration

• With the locked static design open in memory, read in post-synthesis checkpoints for the other two Reconfigurable Modules.

read\_checkpoint -cell inst\_shift Synth/shift\_left/shift\_synth.dcp

read\_checkpoint -cell inst\_count Synth/count\_down/count\_synth.dcp

• Optimize, place, and route the design. Notice the Partition Pins (interface points between static and dynamic regions)

opt\_design

place\_design

route\_design

• Save the full design checkpoint and create report files:

write\_checkpoint -force Implement/Config\_shift\_left\_count\_down/top\_route\_design.dcp

report\_utilization -file Implement/Config\_shift\_left\_count\_down/top\_utilization.rpt

report\_timing\_summary -file Implement/Config\_shift\_left\_count\_down/top\_timing\_summary.rpt

• At this point, you have implemented the static design and all Reconfigurable Module variants. This process would be repeated for designs that have more than two Reconfigurable Modules per RP, or more RPs. Close the current design:

close\_project

#### 3.1.7 Generate Bitstreams

• Run the pr\_verify command from the Tcl Console:

pr\_verify Implement/Config\_shift\_right\_count\_up/top\_route\_design.dcp

Implement/Config\_shift\_left\_count\_down/top\_route\_design.dcp

• Read the first configuration into memory:

#### open\_checkpoint Implement/Config\_shift\_right\_count\_up/top\_route\_design.dcp

• Generate full and partial bitstreams for this design.

write\_bitstream -force -file Bitstreams/Config\_RightUp.bit

close\_project

- Notice the three bitstreams have been created:

- Config\_RightUp.bit This is the power-up, full design bitstream.

- Config\_RightUp\_pblock\_inst\_shift\_partial.bit This is the partial bit file for the shift\_right module.

- Config\_RightUp\_pblock\_inst\_count\_partial.bit This is the partial bit file for the count\_up module.

- Read the Second configuration into memory:

#### open\_checkpoint Implement/Config\_shift\_left\_count\_down/top\_route\_design.dcp

• Generate full and partial bitstreams for this design.

#### write\_bitstream -force -file Bitstreams/Config\_LeftDown.bit

#### close\_project

• Generate a full bitstream with a blackbox for the RP, plus blanking bitstreams for the RMs, these can be used to erase an existing configuration to reduce power consumption:

#### open\_checkpoint Checkpoint/static\_route\_design.dcp

update\_design -cell inst\_count -buffer\_ports

update\_design -cell inst\_shift -buffer\_ports

place\_design

route\_design

write\_checkpoint -force Checkpoint/Config\_black\_box.dcp

write\_bitstream -force -file Bitstreams/config\_black\_box.bit

close\_project

#### 3.1.8 Partial Reconfiguration of the FPGA

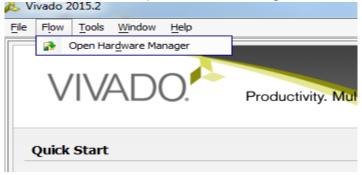

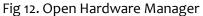

• From the main Vivado IDE, select Flow>Open Hardware Manager.

• Select Open Target >open new target on the green banner. Follow the steps in the wizard to establish communication with the board.

| 🚴 Vivado 2015.2                      |       |                             |   |     |   |         |  |  |  |  |

|--------------------------------------|-------|-----------------------------|---|-----|---|---------|--|--|--|--|

| <u>File Edit Flow Tools Window L</u> | .ayou | t <u>V</u> iew <u>H</u> elp |   |     |   | Q, y Se |  |  |  |  |

| 🏄 🖻 i in 🕫 🐚 🐂 🗙 i 💸                 | 9     | 😬 Default Layout            |   | - X | ۰ | *       |  |  |  |  |

| Hardware Manager - unconnected       |       |                             |   |     |   |         |  |  |  |  |

| (i) No hardware target is open. Open | targe | <u>:t</u>                   |   |     |   |         |  |  |  |  |

| Hardware                             | ₹,    | Auto Connect                |   |     |   |         |  |  |  |  |

| < 조 ≑                                |       | Recent Targets              | • |     |   |         |  |  |  |  |

|                                      |       | Closed Targets              | ► |     |   |         |  |  |  |  |

|                                      | È     | Open New Target             |   |     |   |         |  |  |  |  |

| No content                           |       |                             |   |     |   |         |  |  |  |  |

| Properties                           |       | _ 🗆 🖻 ×                     |   |     |   |         |  |  |  |  |

| 🗻 🔺 💽 🕨                              |       |                             |   |     |   |         |  |  |  |  |

Fig 13. Open New Target

- Select **Program device** on the green banner and pick the xc7z020\_1. Navigate to the Bitstreams folder to select Config\_RightUp.bit, then click OK to program the device.

- You should now see the bank of GPIO LEDs performing two tasks. Four LEDs are performing a counting-up function (MSB is on the left), and the other four are shifting to the right. Note the amount of time it took to configure the full device.

At this point, you can partially reconfigure the active device with any of the partial bitstreams that you have created.

- Select **Program device** on the green banner again. Navigate to the Bitstreams folder to select Config\_LeftDown\_pblock\_inst\_shift\_partial.bit, then click **OK** to program the device.

- The shift portion of the LEDs has changed direction, but the counter kept counting up, unaffected by the reconfiguration. Note the much shorter configuration time.

- Select **Program device** on the green banner again. Navigate to the Bitstreams folder to select Config\_LeftDown\_pblock\_inst\_count\_partial.bit, then click **OK** to program the device.

- The counter is now counting down, and the shifting LEDs were unaffected by the reconfiguration. This process can be repeated with the Config\_RightUp partial bit files to return to the original configuration, or with the blanking partial bit files to stop activity on the LEDs (they will stay on).

<sup>\*</sup>This document is based on the Xilinx document UG947: Vivado Design Suite Tutorial on Partial Reconfiguration